责任编辑:

王王木木

时间:2024-02-04

来源:转载于: 作者:凡亿教育 https://www.bilibili.com/read/cv22689571/ 出处:bilibili

责任编辑:

王王木木

时间:2024-02-04

来源:转载于: 作者:凡亿教育 https://www.bilibili.com/read/cv22689571/ 出处:bilibili

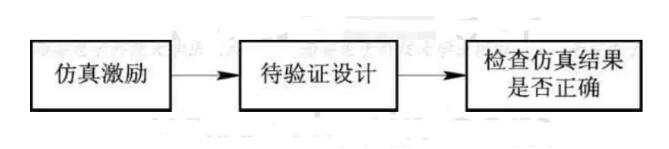

仿真模拟是IC设计的重要环节,但很多小白初学电子设计总会跳过仿真直接测试运行,导致电路崩溃失败,所以有必要进行仿真吗?仿真有什么用吗?如何做好仿真?接下来看看吧!

如图所示,仿真是IC功能验证的主要手段,该图是仿真的基本原理。

除了功能检查,用仿真方法还可以检查系统的时序,与静态时序方法相比,仿真的方法更为直观,能较为真实的模拟出电压发生变化、串扰及毛刺、电容耦合等各种情形下电路的运行情况,其缺点是运行时间较长,且时序检查不完整。

仿真贯穿了IC系统设计的整个阶段。

1、系统设计阶段的仿真

在系统级设计阶段,通过行为仿真,可以达到下述目的:

分析算法是否正确;

验证性能是否满足要求;

验证系统划分是否合理。

系统级设计可大致分为浮点数算法设计、定点数算法设计、架构设计等几个步骤。在每一步都可以进行系统仿真。

系统级的仿真可采用数据流仿真方法(不包括时间信息)和基于周期的仿真方法。

在系统中,通常用SystemC/C /Matlab来描述系统模型。系统模型可作为后续阶段验证的参考。如在RTL设计中,可利用系统模型的输出结果作为参考基准,检查RTL设计得到的结果是否正确。

2、逻辑/电路设计阶段的仿真

逻辑设计阶段的仿真分RTL仿真与门级仿真两种,前者是验证系统功能是否正确的重要手段。在RTL仿真中,如何合理构造testbench、如何进行“correr case”的验证,是困扰设计者的难题,也是目前的验证热点。

一个测试平台应包括如下几个部分:大测试设计、Stimulus(用于生成激励向量)、Monitors(用于监控接口上的活动)、响应比较电路(用于检查设计的输出是否与预期一致)。

门级仿真速度较慢,通常只是作为一种辅助手段来检查时序是否满足要求,所以通常只需运行很少的几种激励即可。

在激励设计阶段,目前仍有许多成熟的仿真工具,如NC Simulator及VCS等,他们都属于事件驱动的仿真工具,即支持RTL仿真也支持门级仿真。

仿真方法存在测试覆盖率低的缺点,厂商们利用形式验证中“断言”的概念,提出了“基于断言的仿真”方法。

此外,也有人尝试采用符号仿真的方法,不过应用量比较少。

对于模拟电路,通常采用Hspice进行仿真。对于特定应用的电路,有一些特定的仿真工具,例如在分析射频(RF)电路时,Cadence的Spectre比较实用。

在数/模混合设计中,往往需要协同验证数字电路和模拟电路。这时候,需要用到混合仿真软件。

目前,混合仿真软件是将逻辑仿真器与电路仿真器结合起来协同工作。模拟部分通常用verilogA来建模。